易翔(华南理工大学微电子学院博导) 0 0

易翔,男,博士,毕业于南洋理工大学,先后于南洋理工大学和麻省理工学院开展博士后研究工作。主要研究方向为射频、毫米波和太赫兹频率综合器、通信和雷达收发机集成电路设计。-

中文名:易翔 民族: 出生地: 毕业院校:南洋理工大学 学位/学历:博士 职业:教师 专业方向: 职务:华南理工大学微电子学院博导 学术代表作: 主要成就:

人物经历

教育经历

2002.09 - 2006.06华中科技大学学士

2006.09 - 2009.06华南理工大学硕士

2009.08 - 2014.07南洋理工大学博士

2014.07 - 2017.07南洋理工大学博士后

2017.07 - 2020.09麻省理工学院博士后

工作经历

2021.01-华南理工大学特聘教授

主要成就

科研成就

新加坡教育部Tier 2项目“先高分辨率超低功耗集成成像器”,2013.7-2016.06 负责人

新加坡教育部Tier 1项目“先进CMOS工艺的单片太赫兹无源元件:从基础研究到集成电路应用”,2016.11-2017.07 负责人

新加坡横向项目(格罗方德)“基于氮化镓的DC-DC转换器电路设计”,2016.06-2017.07 负责人

新加坡横向项目(华为)“下一代无线局域网802.11ax的收发机芯片研发”,2014.07-2017.07 共同主持

新加坡横向项目(台达电子)“用于内容驱动学习媒体传输的无线异构网络收发器芯片”,2016.07-2017.07 共同主持

美国横向项目(台积电)“芯片级太赫兹三维成像雷达”,2017.07-2020.09 负责人

美国横向项目(林肯实验室)“全双工收发机”,2018.10-2020.09 负责人

美国横向项目(德州仪器)“芯片级分子钟”,2017.07-2020.09 核心成员

发表论文

[1]X. Yi, J. Wang, C. Wang, K. E. Kolodziej and R. Han, “Realization of In-Band Full-Duplex Operation at 300 K and 4.2 K Using Bilateral Single-Sideband Frequency Conversion,” IEEE J. Solid-State Circuits, accepted.

[2]X. Yi, C. Wang, X. Chen, J. Wang, J. Grajal, and R. Han, A 220-to-320-GHz FMCW Radar in 65-nm CMOS Using A Frequency-Comb Architecture, IEEE J. Solid-State Circuits, vol. 65, no. 2, pp.327–339, Feb. 2021.

[3]K. Yang, X. Yi, C. C. Boon, Z. Liang, G. Feng, C. Li, B. Liu, A Parallel Sliding-IF Receiver Front-End with Sub-2 dB Noise Figure for 5-6 GHz WLAN Carrier Aggregation, IEEE J. Solid-State Circuits,vol. 56, no. 2, pp.392–403, Feb. 2021.

[4]C. Wang, X. Yi, M. Kim, Q. Yang and R. Han, A Terahertz Molecular Clock on CMOS Using High-Harmonic-Order Interrogation of Rotational Transition for Medium/Long-Term Stability Enhancement, IEEE J. Solid-State Circuits, vol. 56, no. 2, pp.566–580, Feb. 2021.

[5]X. Yi, J. Wang, C. Wang, K. E. Kolodziej and R. Han, “A 3.4~4.6-GHz In-Band Full-Duplex Front-End in CMOS Using A Bi-Directional Frequency Converter,” in RFIC Symp. Dig. Papers, Jun. 2020, pp. 47–50.

[6]X. Yi, C. Wang, M. Lu, J. Wang, J. Grajal and R. Han, A Terahertz FMCW Comb Radar in 65nm CMOS with 100GHz Bandwidth, in IEEE ISSCC Dig. Tech. Papers, Feb. 2020, pp. 90–91.

[7]C. Wang, X. Yi, M. Kim and R. Han, Sub-THz CMOS Molecular Clock with 43ppt Long-Term Stability Using High-Order Rotational Transition Probing and Slot Array Couplers, in IEEE ISSCC Dig. Tech. Papers, Feb. 2020, pp. 448–449.

[8]X. Yi, Z. Liang, C.C. Boon, G. Feng, F. Meng, and K. Yang, “An Inverted Ring Oscillator Noise-Shaping Time-to-Digital Converter with In-band Noise Reduction and Coherent Noise Cancellation, IEEE Trans. on Circuits and Systems-I: Regular Papers, vol. 67, no. 2, pp. 686–698, Feb. 2020.

[9]B. Liu, X. Yi, K. Yang, Z. Liang, G. Feng, P. Choi, C. C. Boon, and C. Li, “A Carrier Aggregation Transmitter Front-End for 5-GHz WLAN 802.11ax Application in 40nm CMOS,” IEEE Trans. Microw. Theory Tech., vol. 68, no. 1, pp. 264–276, Jan. 2020.

[10]C. Li, X. Yi, C. C. Boon, and K. Yang, “A 34 dB Dynamic Range 0.7 mW Compact Switched-Capacitor Power Detector in 65 nm CMOS,” IEEE Trans. on Power Electronics, vol. 34, no. 10, pp. 9365–9368, Oct. 2019.

[11]X. Yi, Z. Liang, G. Feng, F. Meng, C. Wang, C. Li, K. Yang, B. Liu, and C. C. Boon, “A 93.4-to-104.8GHz 57mW fractional-N cascaded PLL with true in-phase injection-coupled QVCO in 65nm CMOS Technology,” IEEE Trans. Microw. Theory Tech., vol. 67, no. 6, pp.2370–2381, Jun. 2019.

[12]C. Wang, X. Yi, J. Mawdsley, M. Kim, Z. Wang, R. Han, “An on-chip fully-electronic molecular clock based on sub-terahertz rotational spectroscopy,” Nature Electronics, Vol. 1, No. 7, Jul. 2018.

[13]X. Yi, K. Yang, Z. Liang, B. Liu, K. Devrishi, C. C. Boon, C. Li, G. Feng, D. Regev, S. Shilo, F. Meng, H. Liu, J. Sun, G. Hu, and Y. Miao, “A 65nm CMOS carrier-aggregation transceiver for IEEE 802.11 WLAN applications,” in RFIC Symp. Dig. Papers, May. 2016, pp.67–70.

[14]X. Yi, Z. Liang, G. Feng, C. C. Boon, and F. Meng, “A 93.4-to-104.8 GHz 57 mW fractional-N cascaded sub-sampling PLL with true in-phase injection-coupled QVCO in 65 nm CMOS,” in RFIC Symp. Dig. Papers, May 2016, pp.122–125.

[15]X. Yi, C. C. Boon, H. Liu, J. Lin, and W. M. Lim, “A 57.9-to-68.3 GHz 24.6 mW frequency synthesizer with in-phase injection-coupled QVCO in 65 nm CMOS Technology,” IEEE J. Solid-State Circuits, vol. 49, no. 2, pp.347–359, Feb. 2014.

[16]X. Yi, C. C. Boon, J. Sun, N. Huang, and W. M. Lim, “A low phase noise 24/77 GHz dual-band sub-sampling PLL for automotive radar applications in 65 nm CMOS technology,” in Proc. ASSCC, Nov. 2013, pp. 417–420.

[17]X. Yi, C. C. Boon, H. Liu, J. Lin, J. C. Ong, and W. M. Lim, “A 57.9-to-68.3GHz 24.6mW frequency synthesizer with in-phase injection-coupled QVCO in 65nm CMOS,” in IEEE ISSCC Dig. Tech. Papers, Feb. 2013, pp. 354–355.

[18]X. Yi, C. C. Boon, J. Lin, and W. M. Lim, “A 100 GHz transformer-based varactor-less VCO with 11.2% tuning range in 65nm CMOS technology,” in Proc. ESSCIRC, Sep. 2012, pp. 293–296.

社会任职

IEEE高级会员

IEEE JSSC、TMTT、TCAS-I等多个国际期刊审稿人

ISCAS评审委员会委员

参考资料

相关阅读

声明

本站上发表的所有内容,均为原作者的观点,不代表姐的欢喜网的立场,也不代表姐的欢喜网的价值判断。百科的词条(含所附图片)系由本站或网友上传,如果涉嫌侵权,请与客服联系,我们将按照法律之相关规定及时进行处理。未经许可,禁止商业网站等复制、抓取本站内容。

人物:何小鹏简介

人物:何小鹏简介 人物:孟晚舟简介

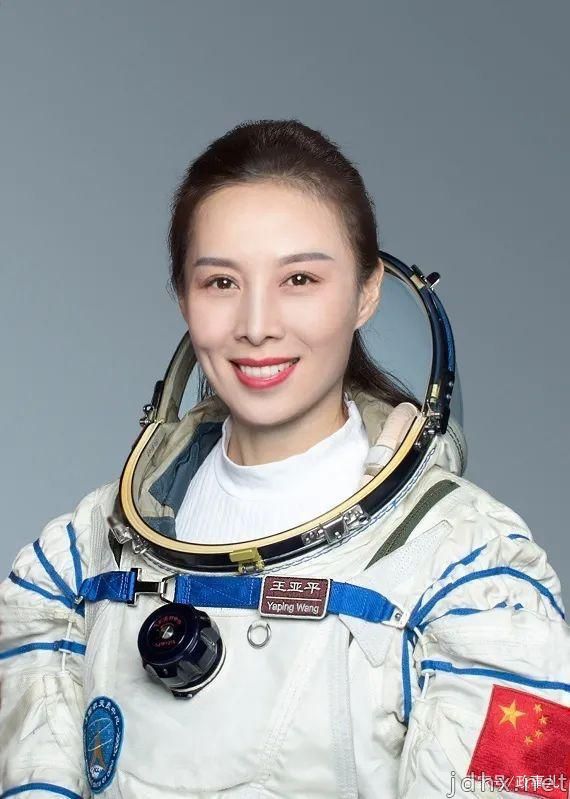

人物:孟晚舟简介 王亚平

王亚平